Hi, I’m Yan Cheng (YC)! 👋

I am a CPU Design Verification engineer at Apple, working in Santa Clara, CA.

Prior to Apple, I graduated from the University of Michigan, Ann Arbor with a Bachelor’s degree in Computer Engineering. I have achieved a 3.71 GPA over my entire tertiary education, completing technical courses such as Computer Architecture, Parallel Computer Architecture, MicroArchitecture, Operating Systems, Integrated Circuits, GPU Programming, Logic Design (Verilog) and many more.

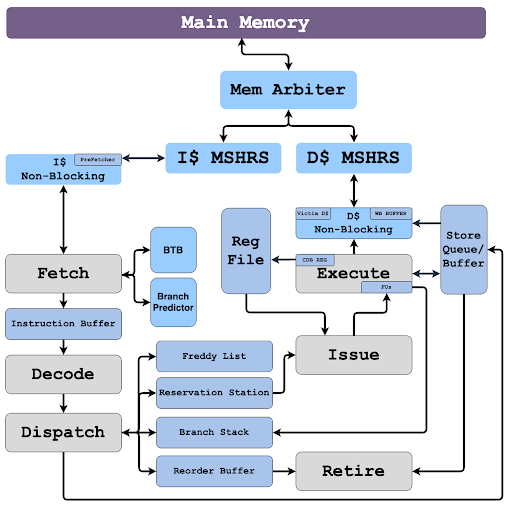

Throughout my college years, I have had several internship and working experiences from AMD, Efinix Inc, and UMich, working in domains such as RTL design/verification, post-silicon validation, firmware engineering and tech research. I also have had the opportunity to work on many cool projects over my college years, including designing a MIPS R10000K based RISC-V Processor, redesigning a Flash Attention Accelerator, architecting a hardware accelerator for k Nearest Neighbour Search, designing a SystemVerilog IP core library, and many more (check out the Projects tab).

Overall, I would describe my skillsets and experiences to be in the following domain:

- Computer Architecture 📲

- RTL Design and Verification 🖥️

- Verilog/SystemVerilog/VHDL 🧑💻

- FPGA/ASIC Logic Design 🧠

Feel free to connect or reach out!

My Passion 🔥

Growing up, I was always fascinated by computers and technology, curious about how these devices worked and were designed. That curiosity naturally led me to pursue computer engineering and sparked a deep passion for digital logic design and computer architecture. Over time, I’ve explored this field through hands-on projects ranging from building a MIPS R10K-style out-of-order processor from scratch to designing a four function calculator on Altera FPGA. I find hardware design both intellectually challenging and incredibly rewarding, and I particularly enjoy solving complex hardware problems while pushing the limits of performance through RTL design. This passion has driven me to develop my own IP core library by redesigning soft IP cores in SystemVerilog for improved performance and functionality. These projects have continue to fuel my aspiration to one day contribute to groundbreaking and revolutionary ASIC/FPGA/CPU designs. Check out the projects page for more details on my projects

| Altera FPGA Design | MIPS R10k Processor Diagram |

|---|---|

|  |

Some More Facts About Me 🚀

I am a Malaysian 🇲🇾.

I can speak 4 different languages:

English, Chinese, Malay, Cantonese

Hobbies outside of tech:

- Playing Basketball 🏀 (Even though I am pretty bad at it)

- Watching NFL, NBA, and EPL 📺 (fan of Detroit Lions, Denver Nuggets, and Liverpool FC)

- Diving 🤿 (I am a licensed open water diver)

For more info 📞

Feel free to reach out to me if you would like to know more about me!

Email - yanchengpoon@gmail.com

Linkedin - Yan Cheng Poon